# EV-EP-010A/SH2A SH7211 と USB コントローラ S1R72V27 の接続例

1版 2009年06月24日

# 1. 概要

本アプリケーションノートは、ルネサステクノロジ社製 CPU SH7211 と、セイコーエプソン社製 USB コントローラ S1R72V27 を 使用したシステム設計する際の接続方法について解説します。

なお、本アプリケーションノートは、あくまで設計例の参考であり、動作を保証するものではありません。実際に設計される際には、必ず各デバイスのデータシートを参照いただけますようお願いします。

# 2. SH7211 と S1R72V27 の接続

## 2.1 SH7211 の使用端子

SH7211 と S1R72V27 と接続するために、SH7211 の以下の端子を使用します。

| 端子名      | 入出力 | 機能           | 備考                 |

|----------|-----|--------------|--------------------|

| D[150]   | 1/0 | データバス        |                    |

| A[81]    | 0   | アドレスバス       |                    |

| #CS[x]   | 0   | チップセレクト信号    | 使用する CS 空間のチップセレクト |

| #RD      | 0   | リード信号        |                    |

| #WEO     | 0   | D[70]ライト信号   |                    |

| #WE1     | 0   | D[158]ライト信号  |                    |

| RD/#WR*1 | 0   | リード/ライト信号    |                    |

| CK*2     | 0   | システムクロック出力   | 40MHz とする          |

| #WAIT*1  | 1   | ハードウェアウェイト要求 |                    |

| IRQ[x]   | 1   | 外部割り込み要求     | 割り込み1本             |

| DREQn*3  | 1   | DMA 要求       |                    |

| DACKn*3  | 0   | DMA アクノリッチ   |                    |

- \*1 必須ではありません

- \*2 CK は必要に応じて接続してください。

- \*3 DMA を使用しない場合は必要ありません。

Fig 2.1-1 SH7211 使用端子

\_

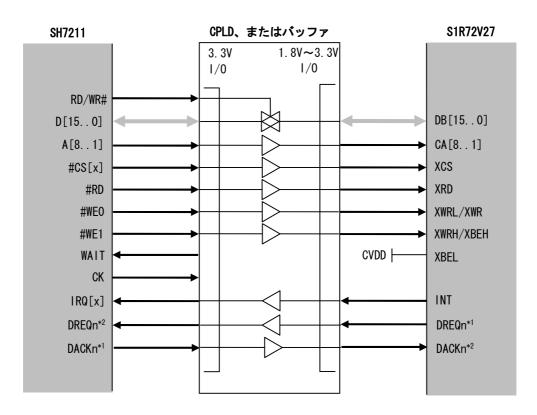

#### 2.2 接続例

以下に SH7211 と S1R72V27 の接続例を示します。

S1R72V27 の Bus モードは Strobe モードとします。

S1R72V27 は CPU I/F I/O 用電圧 (CVDD) 範囲が 1.8~3.3V となっているため、S1R72V27 の CVDD が SH7211 と同じ 3.3V の場合は CPLD またはバッファを省略して各信号を直結することができます。

EV-EP-010A では、CVDD を 2.5V で動作させているため、Xilinx 社製 CPLD「XC2C128-6TGQ144C」を使用しています。 CPLD を使用する場合は、I/0 BANK が 2 つ以上、CVDD 電圧、3.3V の 2 電源で動作し、I/0 数、マクロセル数を満たしているものを選定する必要があります。

ただし、CVDD を 3.3V で使用する場合は 2 電源で動作する CPLD を使用する必要はありません。

- \*1 DMA を使用しない場合は OPEN としてください。

- \*2 DMA を使用しない場合は Inactive レベルに固定してください。

Fig 2.2-1 接続例

### 2.3 バスステートコントローラの設定例

SH7211 から S1R72V27 にアクセスするためには、SH7211 の使用する CS 空間のバスステートコントローラの設定をする必要 があります。バスステートコントローラは、使用するクロックや CPLD、バッファによって設定の変更が必要になる場合が ありますので、ご注意ください。

以下にバスクロック 40MHz の場合のバスステートコントローラ設定例を示します。

| 設定項目                          | 設定値            |

|-------------------------------|----------------|

| ライト-リード/ライト-ライトサイクル間アイドルサイクル数 | 1アイドルサイクル      |

| 別空間リード-ライトサイクル間アイドル数          | 1 アイドルサイクル     |

| 同一空間リード-ライトサイクル間アイドル数         | 1 アイドルサイクル     |

| 別空間リード-リードサイクル間アイドル数          | 1 アイドルサイクル     |

| 同一空間リード-リードサイクル間アイドル指定        | 1 アイドルサイクル     |

| メモリ種類指定                       | 通常空間           |

| エンディアン指定                      | ビッグエンディアンとして動作 |

| データバス幅                        | 16 ビット         |

Fig 2.3-1 CSn 空間パスコントロールレジスタ設定例

| 設定項目                             | 設定値      |

|----------------------------------|----------|

| リードライトアクセスウェイトサイクル数              | 2サイクル    |

| アドレス、CSn アサート→RD、WEn アサート遅延サイクル数 | 0.5 サイクル |

| RD、WEn ネゲート→アドレス、CSn ネゲート遅延サイクル数 | 0.5 サイクル |

Fig 2.3-2 CSn 空間ウェイトコントロールレジスタ設定例

## 2.4 エンディアンの設定

SH7211 はビッグエンディアンで動作します。そのため、S1R72V27 の CPU\_Endian ビットを 0 とし、S1R72V27 をビッグエンディアンに設定する必要があります。

エンディアンについての詳細は、各データシートを参照してください。

# ご注意

- ・本文書の著作権は(株)アルファプロジェクトが保有します。

- ・本文書の内容を無断で転載することは一切禁止します。

- ・本文書の内容は、将来予告なしに変更されることがあります。

- ・本文書に記載されている内容についての質問等のサポートは一切受け付けておりませんのでご了承ください。

- ・本文書の内容については、万全を期して作成いたしましたが、万一ご不審な点、誤りなどお気付きの点がありましたら弊社までご連絡 下さい。

- ・本文書の内容に基づき、アプリケーションを運用した結果、万一損害が発生しても、弊社では一切責任を負いませんのでご了承下さい。

- ・SH-2A および SH7211 は、株式会社ルネサステクノロジの登録商標、商標または商品名称です。

- ・S1R72V27 はセイコーエプソン株式会社の登録商標、商標または商品名称です。

- ・その他の会社名、製品名は、各社の登録商標または商標です。

株式会社アルファプロジェクト 〒431-3114 静岡県浜松市東区積志町834 http://www.apnet.co.jp

E-MAIL: query@apnet.co.jp